Translation Lookaside Buffer (TLB) in OS

Overview

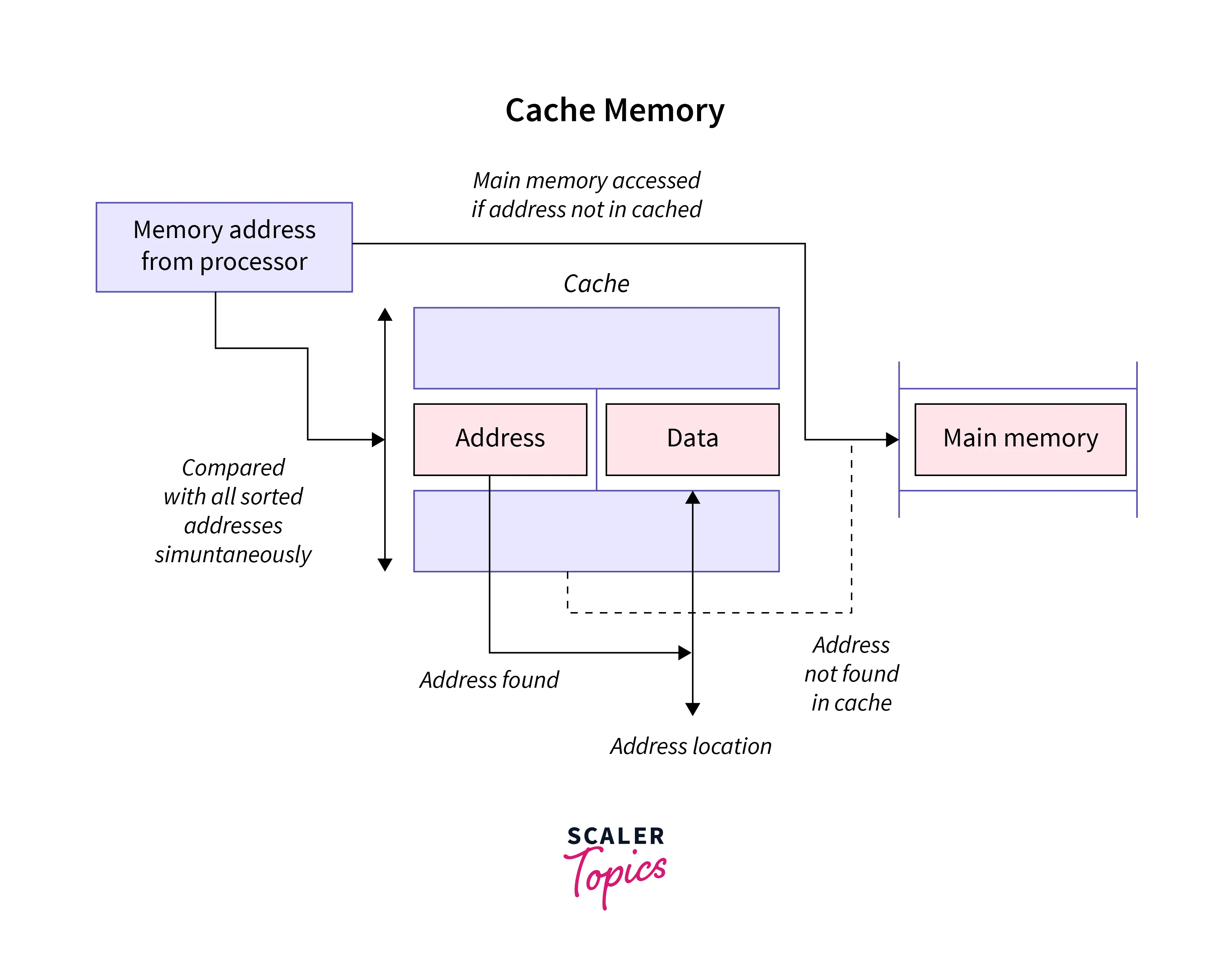

The Translation Lookaside Buffer (TLB) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation of virtual addresses to physical addresses. It reduces memory access latency by storing recently used address mappings and enabling quick lookups. When a program requests memory access, the TLB is consulted first, leading to faster data retrieval if a match (TLB hit) occurs.

What is TLB in OS?

The Translation Lookaside Buffer (TLB) in an operating system is a hardware component that serves as a cache for the virtual-to-physical address translation process. It stores a subset of recently used virtual memory page mappings, making it faster to translate virtual addresses generated by programs into corresponding physical addresses in main memory (RAM). When a program accesses memory, the TLB is consulted, and if it contains the necessary translation, this results in a TLB hit, which significantly speeds up memory access.

Need of TLB

The Translation Lookaside Buffer (TLB) is needed in computer systems, particularly in the context of virtual memory and memory management, for several crucial reasons:

-

Faster Memory Access:

When a program accesses memory, a TLB hit can provide the required translation almost instantly, reducing the time it takes to fetch data from main memory (RAM). This leads to faster program execution and improved system performance.

-

Efficient Use of Memory:

Virtual memory systems allow programs to access more memory than physically available. This reduces contention for memory resources and improves overall system efficiency.

-

Reduced Power Consumption:

Accessing main memory consumes more power compared to accessing the TLB.

-

Minimized Page Table Access:

Without TLB, every virtual-to-physical address translation would require accessing the page table in main memory, which can be time-consuming.

-

Improved System Responsiveness:

TLB helps in maintaining the system's responsiveness. It ensures that memory access operations, which are fundamental to program execution, are as quick as possible, reducing perceived delays and ensuring a smoother user experience.

Steps in TLB Hit

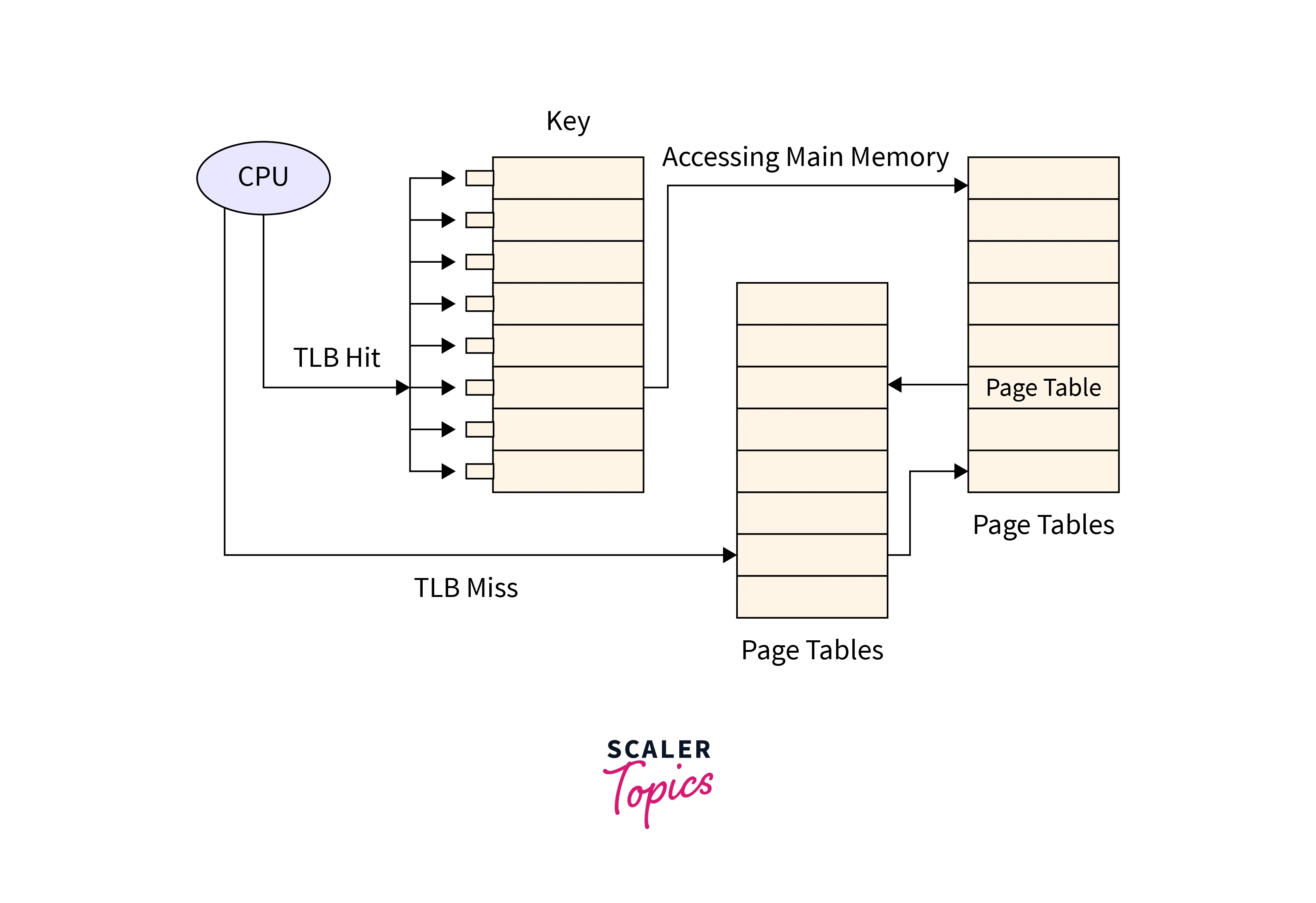

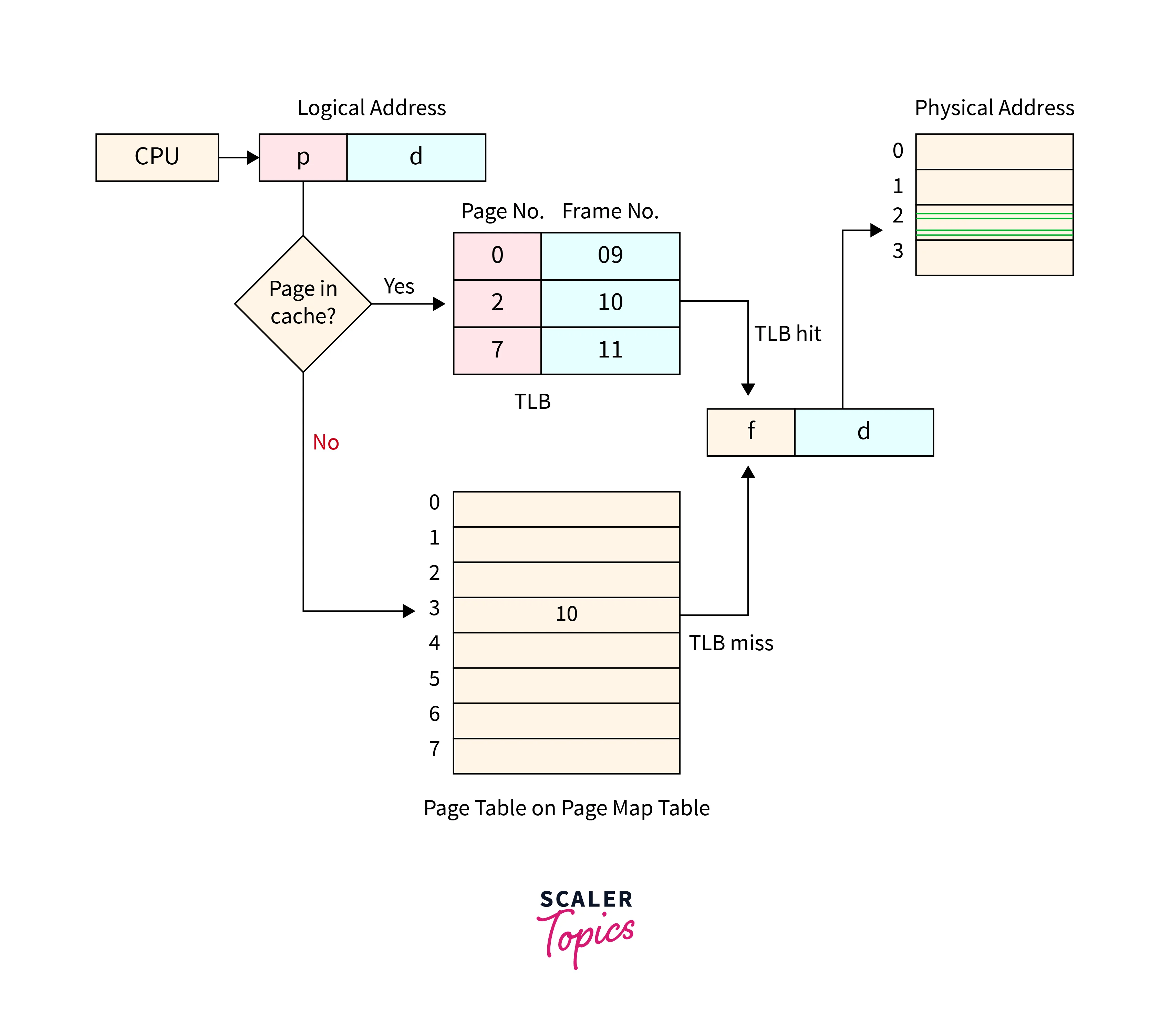

A TLB hit occurs when the Translation Lookaside Buffer (TLB) contains the required virtual-to-physical address translation for a memory access operation. When a TLB hit happens, the steps involved are relatively straightforward and efficient:

- CPU generates a virtual memory address, typically as part of a load or store instruction.

- CPU checks for a match between the generated virtual address and the entries stored in the TLB.

- CPU retrieves the corresponding physical address from the TLB entry. This physical address is used to access the actual data stored in main memory (RAM).

- With the physical address obtained from the TLB, the CPU can access the data in main memory.

Steps in TLB Miss

When a TLB miss occurs, it means that the Translation Lookaside Buffer (TLB) does not contain the required virtual-to-physical address translation for a memory access operation. In this case, the operating system and hardware must perform additional steps to retrieve the necessary translation. Here are the steps involved in a TLB miss:

- A program or process initiates a memory access operation by generating a virtual memory address.

- CPU checks the TLB for a match between the generated virtual address and the entries stored in the TLB. In the case of a TLB miss, no matching entry is found in the TLB.

- Now the CPU must consult the page table, which is a data structure in main memory maintained by the operating system.

- The CPU accesses the page table to retrieve the page table entry corresponding to the virtual address.

- CPU updates the TLB with the new translation information.

- With the translation information from the page table entry, the CPU calculates the physical address corresponding to the original virtual address.

- The CPU can now use the calculated physical address to access the data stored in main memory (RAM).

What is EAT

In the context of a Translation Lookaside Buffer (TLB) in operating systems, "Effective Access Time" (EAT) refers to the total time it takes to complete a memory access operation, taking into account the possibility of both TLB hits and TLB misses. It is a critical metric used to evaluate the overall performance of a memory system with a TLB.

The Effective Access Time (EAT) can be calculated using the following formula:

Where:

-

Hit Time:

This is the time it takes to perform a TLB lookup and retrieve the physical address if there is a TLB hit. In other words, it represents the time it takes for a successful TLB access.

-

Hit Rate:

This is the probability that a memory access results in a TLB hit. It is calculated as the number of TLB hits divided by the total number of memory accesses.

-

Miss Penalty:

This is the time it takes to resolve a TLB miss. It includes the time required to access the page table in main memory and potentially update the TLB with the missing translation.

-

Miss Rate:

This is the probability that a memory access results in a TLB miss. It is calculated as the number of TLB misses divided by the total number of memory accesses.

Advantages of TLB

The Translation Lookaside Buffer (TLB) offers several advantages in computer systems, particularly in the context of memory management and virtual memory. Here are some key advantages of TLB:

-

Faster Memory Access:

TLB accelerates the virtual-to-physical address translation process.

-

Reduced Latency:

By caching frequently used address translations, TLB ensures that frequently accessed data can be retrieved more quickly, improving system responsiveness.

-

Efficient Use of Virtual Memory:

TLB helps efficiently manage this virtual memory by caching frequently used address translations, reducing the need to access the page table in main memory for every memory reference.

-

Lower Power Consumption:

By reducing the frequency of memory accesses, TLB can contribute to lower power consumption, which is particularly important in mobile devices and energy-efficient computing environments.

-

Minimized Page Table Access:

Without TLB, every virtual-to-physical address translation would require accessing the page table in main memory, which can be time-consuming.

-

Improved System Responsiveness:

TLB ensures that memory access operations, which are fundamental to program execution, are as quick as possible, reducing perceived delays and ensuring a smoother user experience.

Limitations of TLB

While the Translation Lookaside Buffer (TLB) provides significant advantages in improving memory access speed and efficiency, it also has certain limitations and challenges:

-

Limited Size:

TLBs have a finite number of entries, and their size is limited by hardware constraints.

-

Management Overhead:

Managing the TLB, including updating and evicting entries, adds some overhead to memory access operations.

-

Complex Hardware:

TLBs require additional hardware components, which can increase the cost and complexity of the CPU or memory management unit.

-

Cache Consistency:

In multiprocessor systems or systems with multiple caches, maintaining cache consistency, including the TLB, can be challenging.

-

TLB Miss Penalty:

When a TLB miss occurs, and the required translation is not in the TLB, it results in a longer memory access time.

-

Inefficient Use of Space:

TLBs may not always be fully utilized, and some entries may become stale if the mapping changes frequently.

FAQs

Q. What is a TLB in computer systems?

A. A TLB, or Translation Lookaside Buffer, is a hardware cache that stores frequently used virtual-to-physical memory address translations, speeding up memory access.

Q. Why do we need a TLB in modern CPUs?

A. CPUs use TLBs to reduce the latency of memory access by providing fast access to frequently used address translations, improving system performance.

Q. What happens when a TLB miss occurs?

A. In case of a TLB miss, the CPU accesses the page table in the main memory to retrieve the required address translation, incurring additional latency.

Q. How can TLB efficiency be improved?

A. TLB efficiency can be enhanced by optimizing TLB size, and replacement policies, and ensuring that frequently accessed address translations are kept in the TLB to minimize TLB misses.

Conclusion

- A Translation Lookaside Buffer (TLB) is a hardware cache designed to store frequently used virtual-to-physical memory address translations, serving as a crucial component in computer systems.

- TLBs are essential in modern CPUs as they significantly reduce memory access latency by providing rapid access to frequently accessed address translations, enhancing overall system performance.

- When a TLB miss occurs, meaning the required translation is not found in the TLB, the CPU must access the page table in the main memory to fetch the needed address translation, resulting in additional latency.

- TLB efficiency can be improved through careful optimization of factors such as TLB size, replacement policies, and the prioritization of frequently accessed address translations, all of which minimize TLB misses.